Année : M2

Durée : 4 à 6 mois

Organisation : ASTC

Contact : Eric Faure

Description : ASTC dispose d’un environnement de modélisation de cœur de processeur avec lequel ont été développés des modèles rapides de cœurs ARM sans cache ; ASTC dispose aussi de modèle de cache ; l’ensemble de ces modèles s’exécute dans un simulateur (VLAB) qui supporte le standard SystemC.

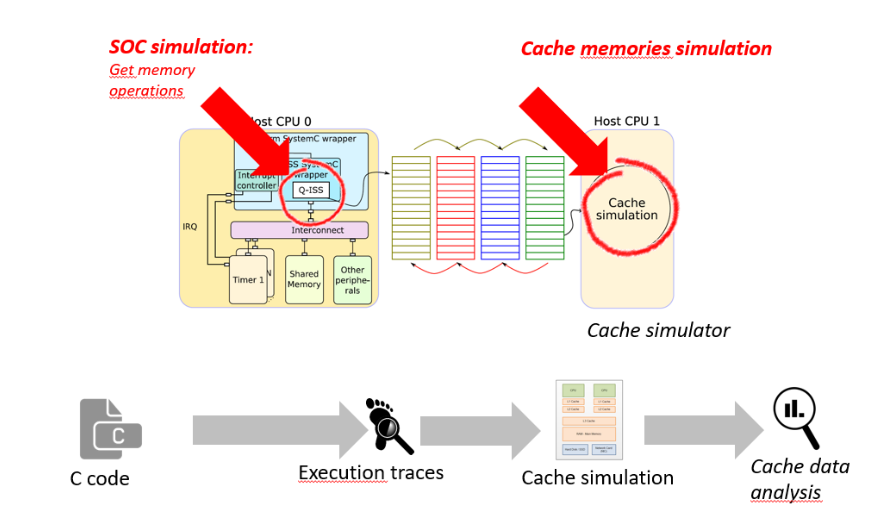

ASTC a participé à un projet collaboratif à L’IRT pour lequel un des sujets était de produire une analyse de l’impact du cache L1 data en utilisant l’outillage suivant :

Le simulateur était un simulateur de SOC basé sur Qemu ;le simulateur de Cache était un modèle ad- hoc.

Le stagiaire devra mettre en œuvre une solution similaire avec les modèles disponibles chez ASTC mais aussi avec des modèles disponibles en open-source comme les modèles de cache Gem5 qui permettront d’étendre les analyses de cache au niveaux L2/L3.

Pour se faire, il développera en C++ les callbacks dans les modèles de cœur d’ASTC pour extraire les informations pertinentes afin de les injecter ensuite dans le simulateur de cache et générer les métriques hit/miss. Le contrôle de la simulation dans l’outil VLAB se fera en programmation Python

Documents : Stage ASTC - Développement d'un outil d'analyse de caches.pdf